We can reduce using boolean algebra, we know how to use truth tables, Karnaugh maps turned out to be a great tool for quick reduction.

But so far we haven't actually designed a system at all...

In order to make the lesson a little more interesting I'm now going to design a logic array for taking a binary number, and displaying the output in hexadecimal.

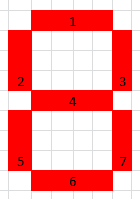

To do this We're going to use a seven segment LED display.

These displays are LED arrays arranged in a figure 8 shape, and can be used to express values by lighting LEDs.

We'll assign each bar of the display a value.

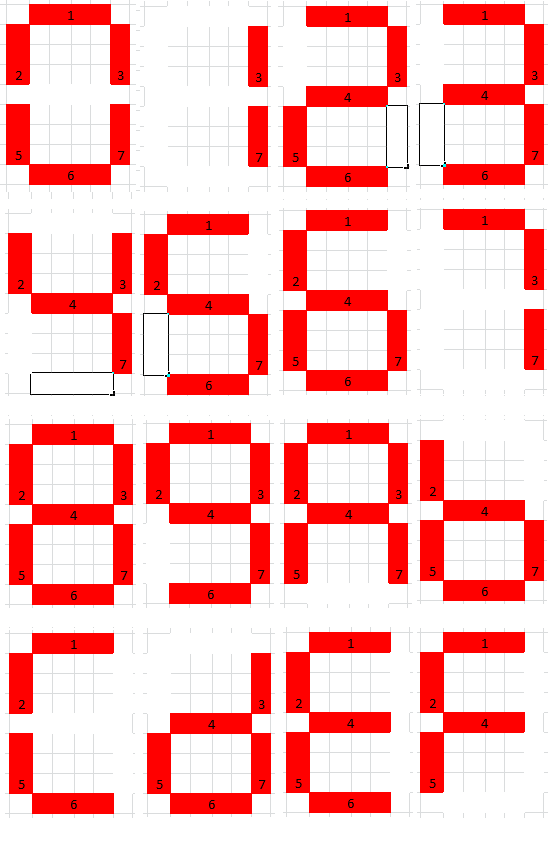

Then we can draw out what we want to display to show for each number.

To do this we draw a truth table, with input states, and our output states for the given input states.

From this truth table we can write out what logical expression we want each of our inputs to be on for.

0 = 0000 = 1 2 3 5 6 7

1 = 0001 = 3 7

2 = 0010 = 1 3 4 5 6

3 = 0011 = 1 3 4 6 7

4 = 0100 = 2 3 4 7

5 = 0101 = 1 2 4 6 7

6 = 0110 = 1 2 4 5 6 7

7 = 0111 = 1 3 7

8 = 1000 = 1 2 3 4 5 6 7

9 = 1001 = 1 2 3 4 6 7

a = 1010 = 1 2 3 4 5 7

b = 1011 = 1 2 4 5 6 7

c = 1100 = 1 2 5 6

d = 1101 = 3 4 5 6 7

e = 1110 = 1 2 4 5 6

f = 1111 = 1 2 4 5

so you can see that segment 1 of the display must be lit for states 0, 2, 3, 5, 6, 7, 8, 9, a, b, c, e and f

our inputs ABCD are listed for each state, so we write down the state of our inputs.

state 0 = /a . /b . /c . /d

state 2 = /a . /b . c . /d

So on and so fourth until we've got all 13 states.

then instead of saying Q1 = State0 OR state2...

we say:

Q1 = /a./b./c./d + /a./b.c./d + /a./b.c.d + /a.b/.c./d + /a.b.c./d + /a.b.c.d + a./b./c./d + a./b./c.d + a./b.c./d + a./b.c.d + a.b./c./d + a.b.c./d + a.b.c.d

We then continue this for the rest of the expected output states.

And reach the following statements:

Output States

Q1 = 0 2 3 5 6 7 8 9 a b c e f

Q2 = 0 4 5 6 8 9 a b c e f

Q3 = 0 1 2 3 4 7 8 9 a d

Q4 = 2 3 4 5 6 8 9 a b d e f

Q5 = 0 2 6 8 a b c d e f

Q6 = 0 2 3 5 6 8 9 b c d e

Q7 = 0 1 3 4 5 6 7 8 9 a b e f

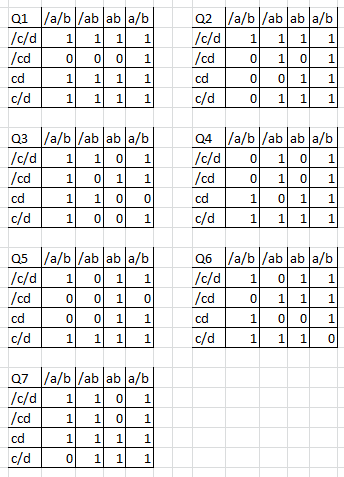

Q1 = /a./b./c./d + /a./b.c./d + /a./b.c.d + /a.b./c./d + /a.b.c./d + /a.b.c.d + a./b./c./d + a./b./c.d + a./b.c./d + a./b.c.d + a.b./c./d + a.b.c./d + a.b.c.d

Q2 = /a./b./c./d + /a.b./c./d + /a.b./c.d + /a.b.c./d + a./b./c./d + a./b./c.d + a./b.c./d + a./b.c.d + a.b./c./d + a.b.c./d + a.b.c.d

Q3 = /a./b./c./d + /a./b./c.d + /a./b.c./d + /a./b.c.d + /a.b./c./d + /a.b.c.d + a./b./c./d + a./b./c.d + a./b.c./d + a.b./c.d

Q4 = /a./b.c./d + /a./b.c.d + /a.b./c./d + /a.b./c.d + /a.b.c./d + a./b./c./d + a./b./c.d + a./b.c./d + a./b.c.d + a.b./c.d + a.b.c./d + a.b.c.d

Q5 = /a./b./c./d + /a./b.c./d + /a.b.c./d + a./b./c./d + a./b.c./d + a./b.c.d + a.b./c./d + a.b./c.d + a.b.c./d + a.b.c.d

Q6 = /a./b./c./d + /a./b.c./d + /a./b.c.d + /a.b./c.d + /a.b.c./d + a./b./c./d + a./b./c.d + a./b.c.d + a.b./c./d + a.b./c.d + a.b.c./d

Q7 = /a./b./c./d + /a./b./c.d + /a./b.c.d + /a.b./c./d + /a.b./c.d + /a.b.c./d + /a.b.c.d + a./b./c./d + a./b./c.d + a./b.c./d + a./b.c.d + a.b.c./d + a.b.c.d

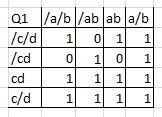

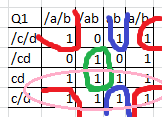

So now we can draw out the karnaugh maps for reducing these statements to their minimal form.

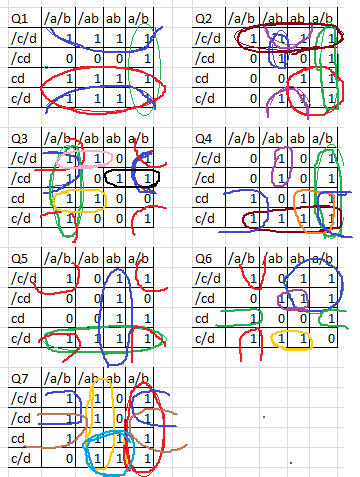

Then we start with looping groups of 1, 2, 4, 8 and 16.

Remembering that maps can loop around the top to the bottom, and that maps can loop left to right, and across the corners. (see Q3, Q5 and Q6 for an example of this):

Q1 = C + /D + (A. /B)

Q2 = (/C . /D) + (B . /D) + (A . C) + (A . /B) + (/A . B . /C)

Q3 = (/A . /B) + (/B . /C) + (/B . /D) + ( /A . /C . /D) + (/A . C . D) + (A . /C . D)

Q4 = (A . /B) + (C . /D) + (A . C) + (/B . C) + (/A . B . /C)

Q5 = (C . /D) + (/B . /D) + (A . B)

Q6 = (A . /C) + (/A . /B . /D) + (/B . C . D) + (B . /C . /D) + (B . C . /D)

Q7 = (A . /B) + (/A . B) + (B . C) + (/B . /C) + (/B . D)

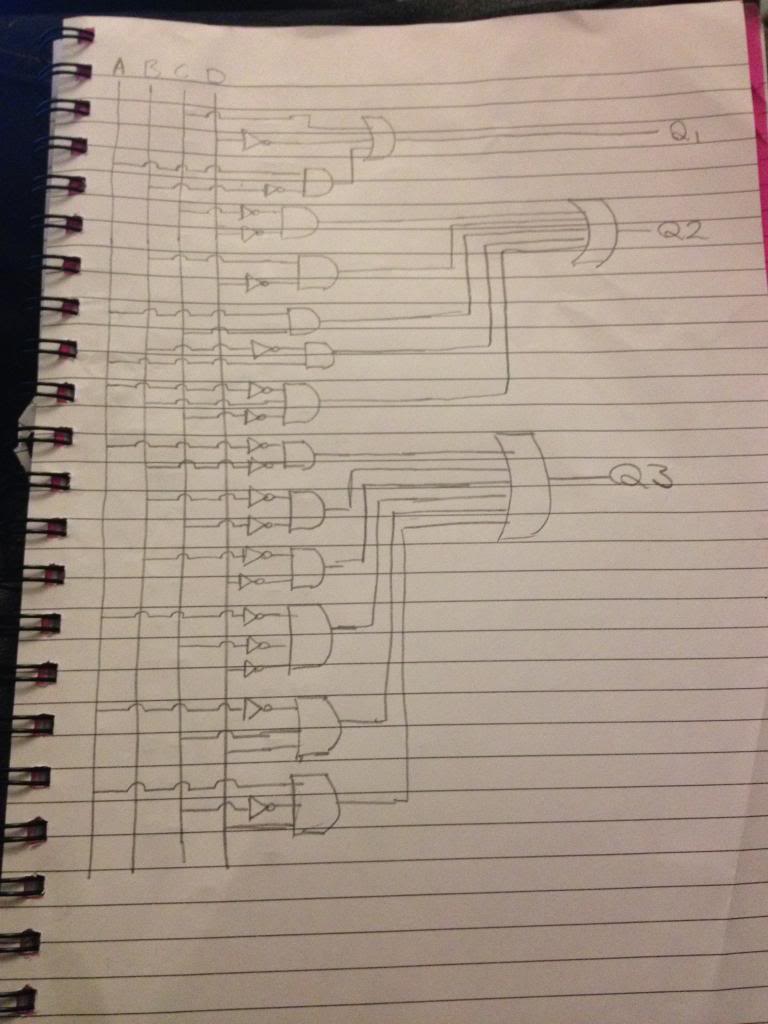

So now we'll build a schematic for this circuit.

There are in total.

40 NOT gates

39 AND Gates, 31 x 2 input gates and 8 x 3 input gates

And of course 7 OR gates of varying input sizes

Note: After reviewing this I've noticed that there is a mistake for the output Q1.

This should have been minimised as so.

if you use the logic derrived in the first part of this post then you'll find that the output for Q1 on states 4 and 5 will be back to front.

e.g. the top bar will light for 4, making it look like a 9 without a tail.

the top bar will not light for 5 making it look like an upside down question mark

No comments:

Post a Comment